# **DRAMA: Exploiting DRAM Buffers for Fun and Profit**

Master Defense Presentation

Michael Schwarz October 13, 2016

Graz University of Technology

# Introduction

# If cache attacks are not possible, is the system secure against microarchitectural side-channel attacks?

• We know "normal" Cache Attacks

1

- Flush+Reload

- Prime+Probe

- Flush+Flush

- We know "normal" Cache Attacks

- Flush+Reload

- Prime+Probe

- Flush+Flush

- · As these attacks became known, countermeasures were developed

- Deactivate Memory Deduplication

- Use multiple CPUs that do not share a cache

• Identify DRAM as a new attack target across CPUs

- Identify DRAM as a new attack target across CPUs

- First fully automated method to reverse engineer DRAM

- Identify DRAM as a new attack target across CPUs

- · First fully automated method to reverse engineer DRAM

- Demonstrate DRAM-based attacks

- Identify DRAM as a new attack target across CPUs

- · First fully automated method to reverse engineer DRAM

- Demonstrate DRAM-based attacks

- DRAM-based template attacks

- Identify DRAM as a new attack target across CPUs

- · First fully automated method to reverse engineer DRAM

- Demonstrate DRAM-based attacks

- DRAM-based template attacks

- Access the internet from a VM without network hardware using a JavaScript covert channel

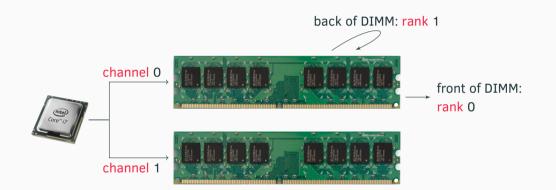

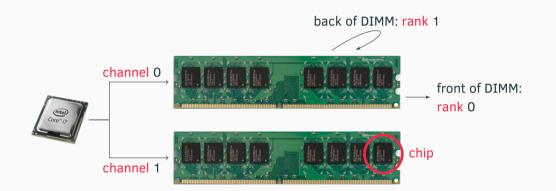

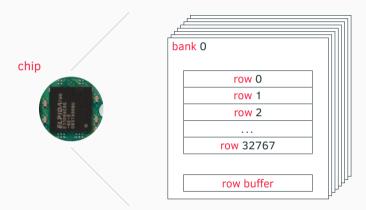

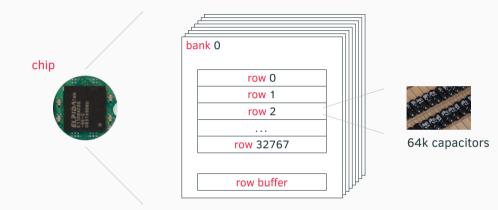

# **DRAM** organization

# **DRAM** organization

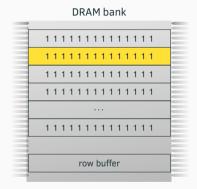

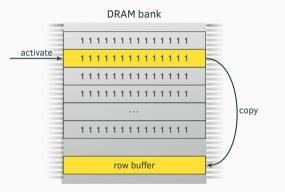

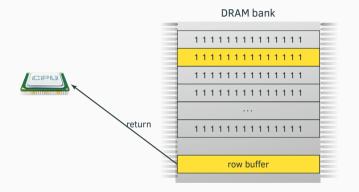

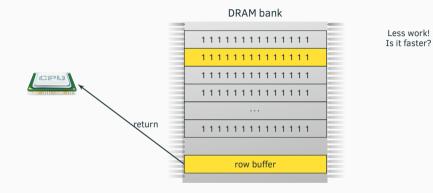

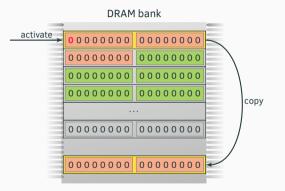

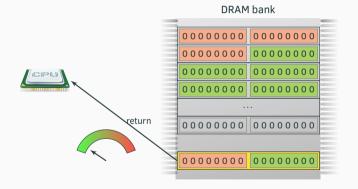

# **Reading from DRAM**

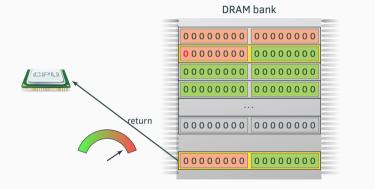

Capacitors discharge when reading bits

- Buffer the bits when reading them from the cells

- · Write the bits back to the cells when done reading

- = Row buffer

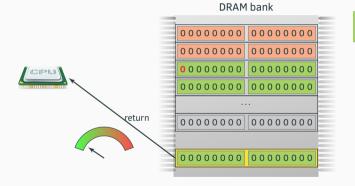

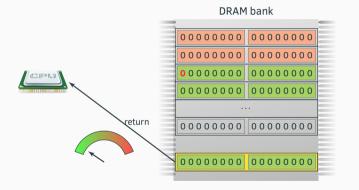

CPU reads row 1, row buffer empty!

CPU reads row 1, row buffer now full!

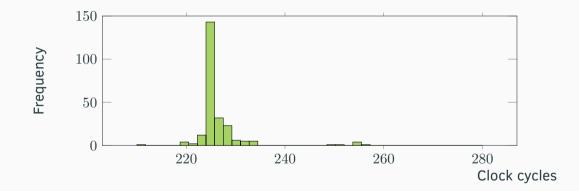

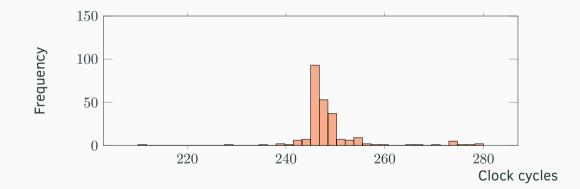

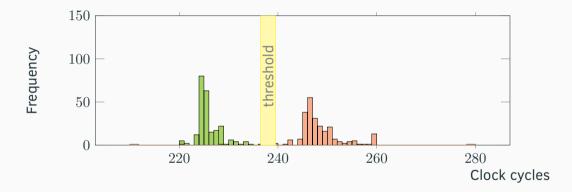

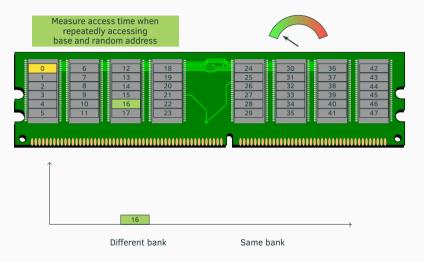

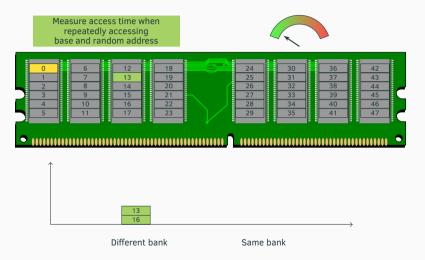

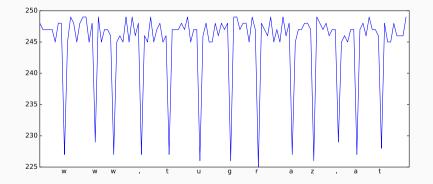

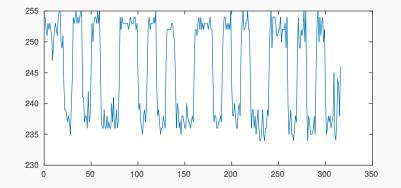

# We can measure a difference

Row hit

# We can measure a difference

Row conflicts

#### We can measure a difference

Difference between row hits (pprox 225 cycles) and row conflicts (pprox 247 cycles)

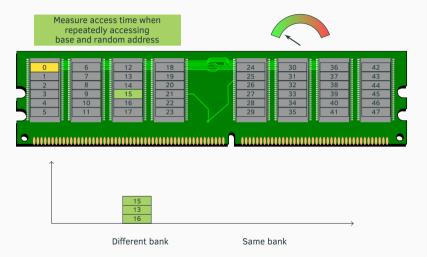

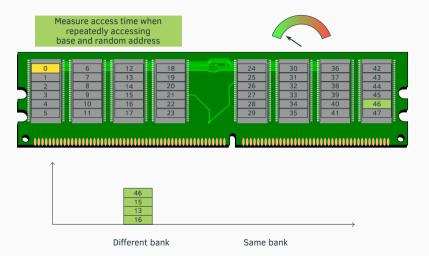

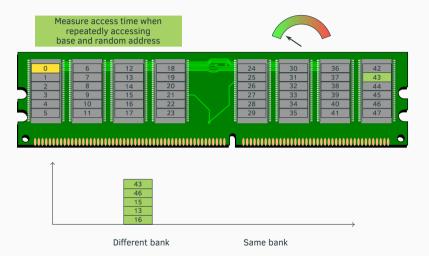

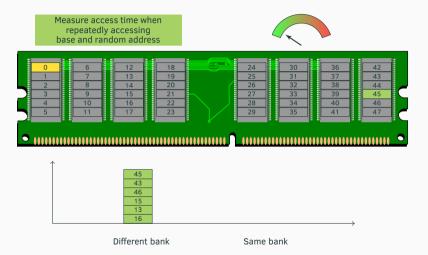

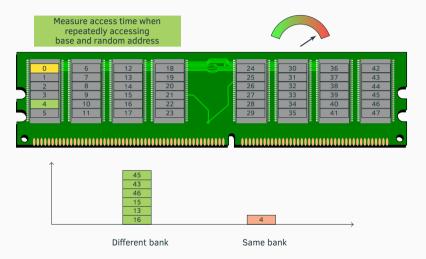

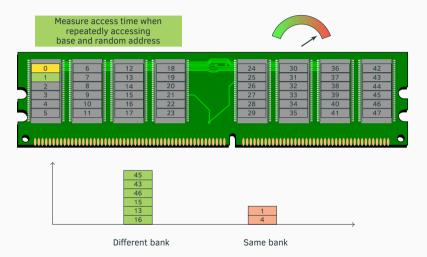

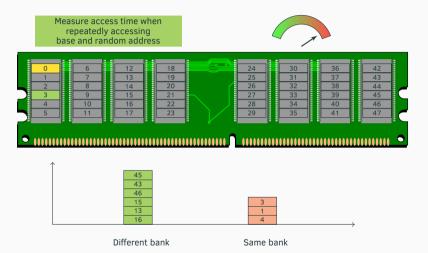

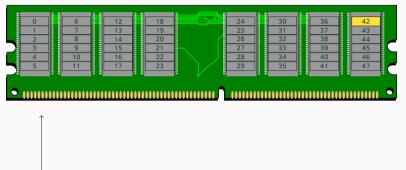

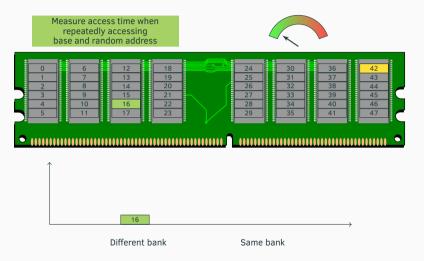

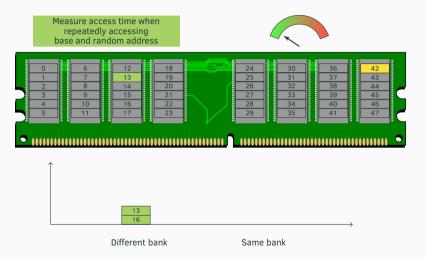

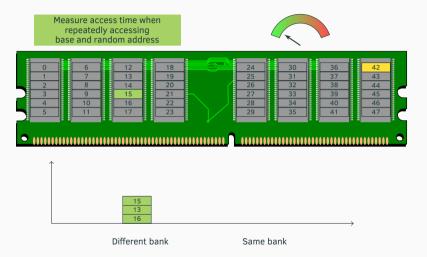

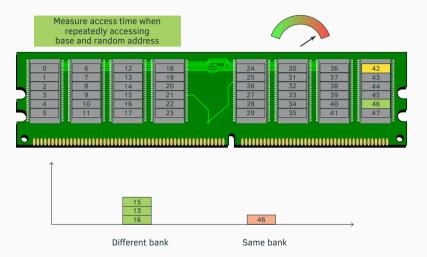

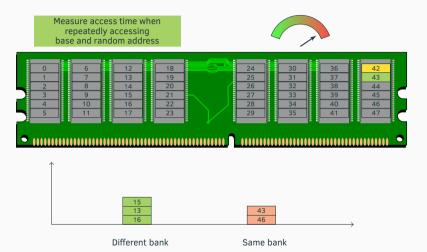

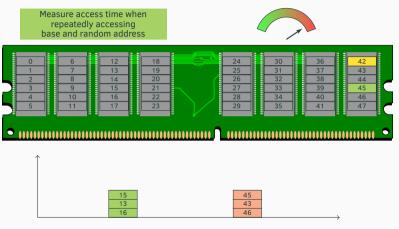

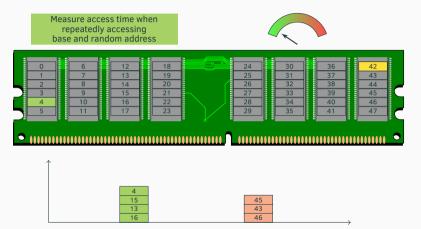

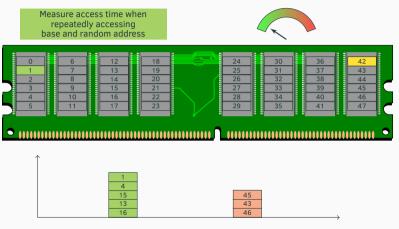

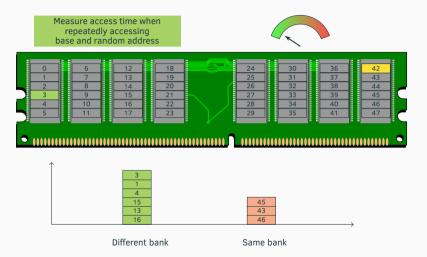

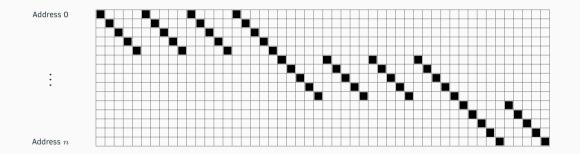

# **Reverse Engineering the Mapping**

Different bank

Same bank

# Select random base address in one bank

Different bank

Same bank

# Select random base address in one bank

Different bank

Different bank

Different bank

Different bank

• Repeat the process for all banks

- Repeat the process for all banks

- For each bank, we have a set of addresses that map to this bank

- Repeat the process for all banks

- For each bank, we have a set of addresses that map to this bank

- · We can see it as a linear equation system

- · Repeat the process for all banks

- For each bank, we have a set of addresses that map to this bank

- We can see it as a linear equation system

- · Solving it gives us the bits used for the mapping functions

- · Repeat the process for all banks

- For each bank, we have a set of addresses that map to this bank

- We can see it as a linear equation system

- Solving it gives us the bits used for the mapping functions

- The alternative: generate every possible XOR function and check if it yields the same result for all addresses in the set

- Repeat the process for all banks

- For each bank, we have a set of addresses that map to this bank

- We can see it as a linear equation system

- · Solving it gives us the bits used for the mapping functions

- The alternative: generate every possible XOR function and check if it yields the same result for all addresses in the set

- This is still very fast (in the order of seconds)

### Results

• We developed a toolkit that reverse engineers the mapping fully automatically

### Results

- We developed a toolkit that reverse engineers the mapping fully automatically

- We tested it on Ivy Bridge, Haswell, Skylake, ARMv7 and ARMv8

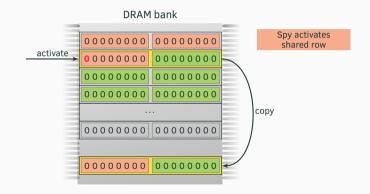

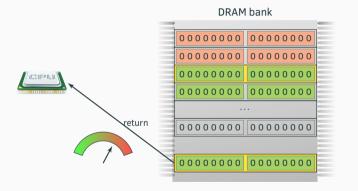

• We want to spy on the behaviour of a victim

- We want to spy on the behaviour of a victim

- The victim will not know that we spy on it

- · We want to spy on the behaviour of a victim

- · The victim will not know that we spy on it

- We can use row hits to get useful information

- · We want to spy on the behaviour of a victim

- · The victim will not know that we spy on it

- We can use row hits to get useful information

- Advantage over cache attacks: it works across CPUs

#### Attack Primitive: Row hit

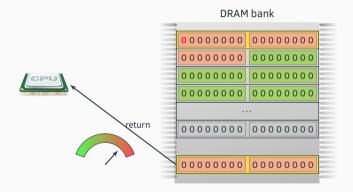

### DRAM bank 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 0000000 00000000 row buffer

Spy activates row O, get copied to row buffer

#### Attack Primitive: Row hit

### DRAM bank 0000000 00000000

...but what if the victim accessed the shared row...

Attack Primitive: Row hit

U.S. Hand

Attack Primitive: Row hit

### DRAM bank 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000 0000000 00000000 0000000 00000000

...before the spy activates it

#### Attack Primitive: Row hit

Row hit, faster

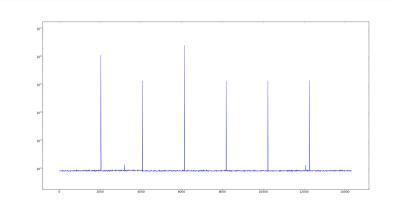

# **Result: Spying on Firefox**

What is a covert communication?

• Two programs would like to communicate

• Two programs would like to communicate but are not allowed to do so

- Two programs would like to communicate but are not allowed to do so

- All "normal" channels are blocked or monitored

- Two programs would like to communicate but are not allowed to do so

- All "normal" channels are blocked or monitored

- They have to find a side channel

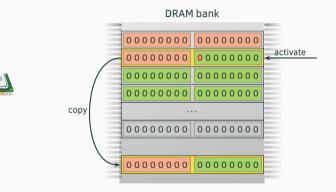

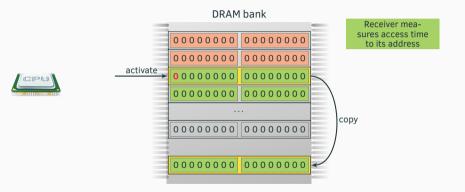

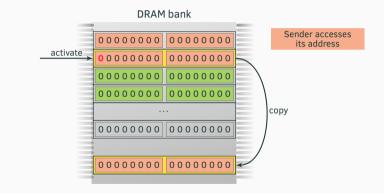

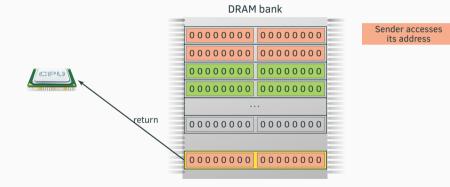

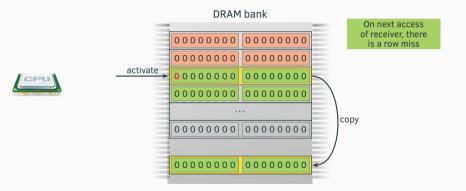

#### Attack Primitive: Row miss

#### DRAM bank

00000000

00000000

00000000

00000000

00000000

00000000

00000000

00000000

....

00000000

00000000

....

000000000

00000000

....

row buffer

Sender and receiver decide on one bank

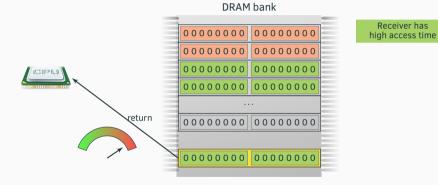

#### Attack Primitive: Row miss

Repeated access always has low access times

• Sender and receiver agree on a bank (can be hardcoded)

- Sender and receiver agree on a bank (can be hardcoded)

- Both sender and receiver select a different row inside this bank

- Sender and receiver agree on a bank (can be hardcoded)

- Both sender and receiver select a different row inside this bank

- Receiver measures access time for this row

- Sender and receiver agree on a bank (can be hardcoded)

- Both sender and receiver select a different row inside this bank

- Receiver measures access time for this row

- Sender can transmit 0 by doing nothing and 1 by causing row conflict

- Sender and receiver agree on a bank (can be hardcoded)

- Both sender and receiver select a different row inside this bank

- Receiver measures access time for this row

- Sender can transmit 0 by doing nothing and 1 by causing row conflict

- If measured timing was "fast" sender transmitted 0.

• Sender and receiver both inside the VM

### **DRAM Covert Channel**

• Sender and receiver both inside the VM

## JavaScript Covert Channel

• JavaScript running in the browser on the host

- JavaScript running in the browser on the host

- Browser acts as receiver

- · JavaScript running in the browser on the host

- Browser acts as receiver

- Sender in VM without internet access

- JavaScript running in the browser on the host

- Browser acts as receiver

- Sender in VM without internet access

- Problem: No addresses in JavaScript

- · JavaScript running in the browser on the host

- Browser acts as receiver

- Sender in VM without internet access

- Problem: No addresses in JavaScript

- $\rightarrow$  Cannot apply DRAM functions

### **The Problem - Physical Addresses**

• Iterate over a large array and measure timing

### **The Problem - Physical Addresses**

- Iterate over a large array and measure timing

- · We can detect the page borders due to pagefaults

• We only have to trick the victim to visit our page

- We only have to trick the victim to visit our page

- Transmission of approximately  $11\,\rm{bit/s}$

- We only have to trick the victim to visit our page

- Transmission of approximately  $11\,\rm{bit/s}$

- Enough to steal keys or passwords

# Conclusion

• We discovered a new attack vector

- We discovered a new attack vector

- Advantage over cache attacks: it works across CPUs

- We discovered a new attack vector

- · Advantage over cache attacks: it works across CPUs

- Demonstrated two use cases:

- · We discovered a new attack vector

- · Advantage over cache attacks: it works across CPUs

- Demonstrated two use cases:

- Spy on other processes

- · We discovered a new attack vector

- · Advantage over cache attacks: it works across CPUs

- Demonstrated two use cases:

- Spy on other processes

- Covert channel across CPUs

- · We discovered a new attack vector

- · Advantage over cache attacks: it works across CPUs

- Demonstrated two use cases:

- Spy on other processes

- Covert channel across CPUs

- Implemented the covert channel in JavaScript

Pessl, P., Gruss, D., Maurice, C., Schwarz, M., and Mangard, S. (2016). DRAMA: Exploiting DRAM addressing for cross-cpu attacks. (USENIX Security 16).

Pessl, P., Gruss, D., Maurice, C., Schwarz, M., and Mangard, S. (2016). DRAMA: Exploiting DRAM addressing for cross-cpu attacks. (USENIX Security 16).

• DRAM covert channel in JavaScript

Pessl, P., Gruss, D., Maurice, C., Schwarz, M., and Mangard, S. (2016). DRAMA: Exploiting DRAM addressing for cross-cpu attacks. (USENIX Security 16).

DRAM covert channel in JavaScript Schwarz, M. and Fogh, A. (2016). DRAMA: How your DRAM becomes a security problem (Black Hat Europe 2016)

Pessl, P., Gruss, D., Maurice, C., Schwarz, M., and Mangard, S. (2016). DRAMA: Exploiting DRAM addressing for cross-cpu attacks. (USENIX Security 16).

- DRAM covert channel in JavaScript Schwarz, M. and Fogh, A. (2016). DRAMA: How your DRAM becomes a security problem (Black Hat Europe 2016)

- Fully automatic DRAM reverse engineering tool

Pessl, P., Gruss, D., Maurice, C., Schwarz, M., and Mangard, S. (2016). DRAMA: Exploiting DRAM addressing for cross-cpu attacks. (USENIX Security 16).

- DRAM covert channel in JavaScript Schwarz, M. and Fogh, A. (2016). DRAMA: How your DRAM becomes a security problem (Black Hat Europe 2016)

- Fully automatic DRAM reverse engineering tool https://github.com/iaik/drama

Thank you for your attention!

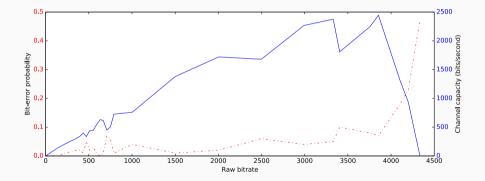

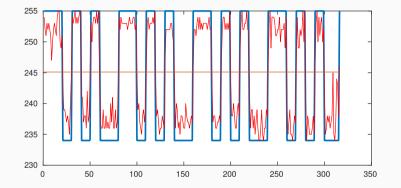

# Additional: Covert Channel Transmission

# The gory details - Eviction

Figure 1: Multiple measurements per bit to have a reliable detection.

Figure 1: Multiple measurements per bit to have a reliable detection.

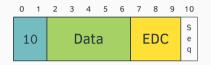

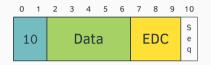

• Communication is based on packets

- Communication is based on packets

- Packet starts with a 2-bit preamble

- Communication is based on packets

- Packet starts with a 2-bit preamble

- Data integrity is checked by an error-detection code (EDC)

- Communication is based on packets

- · Packet starts with a 2-bit preamble

- Data integrity is checked by an error-detection code (EDC)

- Sequence bit indicates whether it is a retransmission or a new packet

# **Additional: Accuracy**

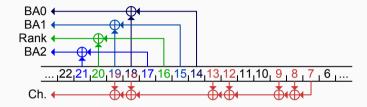

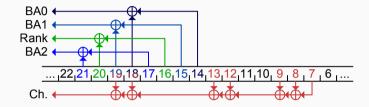

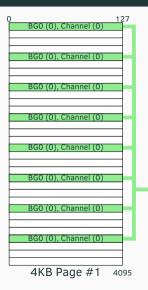

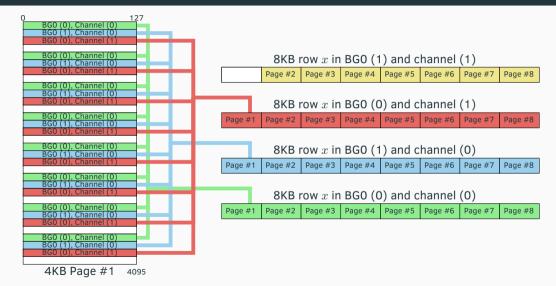

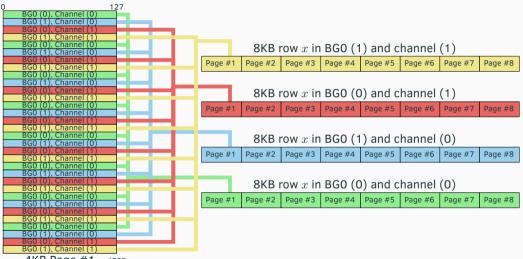

• Not the whole physical page must be in one row

- Not the whole physical page must be in one row

- Depending on the mapping function, a page can be distributed over multiple rows

- Not the whole physical page must be in one row

- Depending on the mapping function, a page can be distributed over multiple rows

- This is the case if address bits 0 to 11 are used for the mapping

- Not the whole physical page must be in one row

- Depending on the mapping function, a page can be distributed over multiple rows

- This is the case if address bits 0 to 11 are used for the mapping

- For example: Skylake uses low bits for channel (bits 8 and 9) and bankgroup (bit 7)

- Not the whole physical page must be in one row

- Depending on the mapping function, a page can be distributed over multiple rows

- This is the case if address bits 0 to 11 are used for the mapping

- For example: Skylake uses low bits for channel (bits 8 and 9) and bankgroup (bit 7)

- One physical page is distributed over 4 rows

#### 8KB row x in BG0 (1) and channel (1)

Page #2

Page #3

Page #4

Page #5

Page #6

Page #7

Page #8

#### 8KB row x in BG0 (0) and channel (1)

Page #2

Page #3

Page #4

Page #5

Page #6

Page #7

Page #8

#### 8KB row x in BG0 (1) and channel (0)

Page #2

Page #3

Page #4

Page #5

Page #6

Page #7

Page #8

#### 8KB row x in BG0 (0) and channel (0)

|  | Page #2 | Page #3 | Page #4 | Page #5 | Page #6 | Page #7 | Page #8 |

|--|---------|---------|---------|---------|---------|---------|---------|

|--|---------|---------|---------|---------|---------|---------|---------|

#### 8KB row x in BG0 (1) and channel (1)

Page #2

Page #3

Page #4

Page #5

Page #6

Page #7

Page #8

#### 8KB row x in BG0 (0) and channel (1)

Page #2

Page #3

Page #4

Page #5

Page #6

Page #7

Page #8

8KB row x in BG0 (1) and channel (0)

Page #2

Page #3

Page #4

Page #5

Page #6

Page #7

Page #8

8KB row x in BG0 (0) and channel (0)

| Page #1 | Page #2 | Page #3 | Page #4 | Page #5 | Page #6 | Page #7 | Page #8 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|---------|---------|---------|---------|---------|---------|---------|---------|

#### 8KB row x in BG0 (1) and channel (1)

Page #2

Page #3

Page #4

Page #5

Page #6

Page #7

Page #8

8KB row x in BG0 (0) and channel (1)

Page #2

Page #3

Page #4

Page #5

Page #6

Page #7

Page #8

8KB row x in BGO (1) and channel (0)

Page #1

Page #2

Page #3

Page #4

Page #5

Page #6

Page #7

Page #8

8KB row x in BG0 (0) and channel (0)

| Page #1 | Page #2 | Page #3 | Page #4 | Page #5 | Page #6 | Page #7 | Page #8 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|---------|---------|---------|---------|---------|---------|---------|---------|

4KB Page #1 4095

# **References** i